Контрольная работа: Мікропроцесорна система та її функціонування

Контрольная работа: Мікропроцесорна система та її функціонування

МIНIСТЕРСТВО ОСВIТИ I НАУКИ УКРАЇНИ

ХАРКIВСЬКИЙ НАЦІОНАЛЬНИЙ УНIВЕРСИТЕТ

РАДIОЕЛЕКТРОНIКИ

Кафедра ЕН

КОНТРОЛЬНА РОБОТА

з дисципліни

"Електронні пристрої"

на тему

МІКРОПРОЦЕСОРНА СИСТЕМА ТА ЇЇ ФУНКЦІОНУВАННЯ

Харків 2010

Визначимо поняття та терміни, які використовуються в мікропроцесорній техніці:

Мікропроцесор (МП) - програмно-керований пристрій, що здійснює процес обробки цифрової інформації і управління ним; побудований на одній або декількох великих інтегральних схемах (ВІС).

Мікропроцесорна ВІС - інтегральна мікросхема, що виконує функцію МП або його частини (ВІС з процесорною організацією, розроблена для побудови мікропроцесорних систем).

Мікропроцесорна система - управляюча інформаційна або інша спеціалізована цифрова система, побудована на базі мікропроцесорних пристроїв.

Мікропроцесорна ЕОМ (мікро-ЕОМ) - це ЕОМ, що складається з мікропроцесора (мікропроцесорів), напівпровідникової пам'яті, засобів зв'язку з периферійними пристроями та джерела живлення, поєднаних загальною несучою конструкцією.

Мікропроцесорний комплект (МПК) - набір мікропроцесорних та інших інтегральних мікросхем, сумісних по конструктивно-технологічному виконанню та призначених для сумісного вживання при побудові мікро-ЕОМ і інших засобів обчислювальної техніки.

Все різноманіття МП зручно розділити на два типи:

- однокристальні МП з фіксованою розрядністю слова та фіксованою системою команд і, як правило, пристроєм управління зі "схемною" логікою;

- багатокристальні (секційні) мікропрограмовані МП із змінною розрядністю слова і з фіксованим набором мікрооперацій.

Мікрокомп'ютери першого типу мають типову структуру типову, яка нагадує організацію звичайних ЕОМ. В ній в явній формі знайшов віддзеркалення принцип обробки даних на основі виконання команд програми. Тому методи роботи з МП першого типу певною мірою подібні методам роботи малих ЕОМ.

Однокристальні МП виконуються з використанням різних МОП-технологій мікроелектроніки, що дозволяють розміщувати на одному кристалі велике число елементарних схем, МОП-транзисторів дякуючи їх унікально малим розмірам і невеликій потужності розсіювання. МОП-структури перших поколінь істотно поступалися в швидкодії біполярним структурам.

Біполярні ВІС (наприклад, з малопотужними ТТЛ-схемами з діодами Шотки) володіли в порівнянні з МОП-ВІС набагато більшою швидкодією, але значно меншою густиною упаковки компонентів на кристалі.

З'явився другий тип МП - багатокристальний біполярний МП, заснований на конструктивному принципі ФУНКЦІОНАЛЬНО-РОЗРЯДНОГО СЛОВА, що пропонує реалізацію на кристалі малорозрядної (2-4 розряди) мікропроцесорної секції (пошарові). В цьому випадку для забезпечення обробки слів заданої розрядності мікропроцесор складається з відповідної кількості однакових кристалів (мікропроцесорних секцій, "слів") об'єднаних мікропрограмним блоком управління, реалізованим на окремих кристалах.

Мікропрограмні багатокристальні МП забезпечують велику гнучкість в досягненні потрібних користувачі характеристик (в першу чергу потрібної швидкодії мікропроцесорного пристрою або мікропроцесорної системи, надаючи користувачу можливість задавати спеціалізовану систему команд, орієнтовану на певне використання. Проте при цьому проектувальник повинен розробляти мікропрограми, які реалізують ці команди, і записати їх в управляючу пам'ять МП.

Згодом різні варіанти поліпшеної МОП-технології дозволили не тільки збільшивши кількість елементів на кристалі, але і випередили по швидкодії МП на основі біполярної технології.

Для внутрішнього опису функціонування МП необхідно охарактеризувати:

- формат оброблюваних даних і команд;

- тип і гнучкість команд;

- способи адресації даних;

- кількість внутрішніх регістрів загального призначення;

- організацію і адресацію стека;

- параметри віртуальної пам'яті;

- інформаційний об’єм пам'яті.

МП також розрізняють:

- по числу ВІС в МП;

- по призначенню;

- по виду оброблюваних вхідних сигналів;

- по організації структури МП схем.

По характеру роботи в часі МП поділяють на синхронні і асинхронні.

Синхронні МП - це МП, в яких початок і кінець виконання операцій задається пристроєм управління ПУ.

Асинхронні МП дозволяють початок виконання кожної наступної операції визначити по сигналу фактичного закінчення виконання попередньої операції.

По організації структури МП системи розрізняють:

- одно магістральні мікро-ЕОМ;

- багато магістральні мікро-ЕОМ.

У одно магістральних мікро-ЕОМ всі пристрої мають однаковий інтерфейс і підключені до єдиної інформаційної магістралі, по якій передаються коди даних, адреси і управляючих сигналів.

У багато магістральних мікро-ЕОМ пристрої групами підключаються до своєї інформаційної магістралі.

По кількості виконуваних програм розрізняють: однопрограмні і багатопрограмні МП.

У однопрограмному МП перехід і виконання наступної програми відбувається після завершення поточної програми.

Багатопрограмний МП дозволяє виконувати одночасно декілька програм.

Основою будь-якої мікропроцесорної системи є МП.

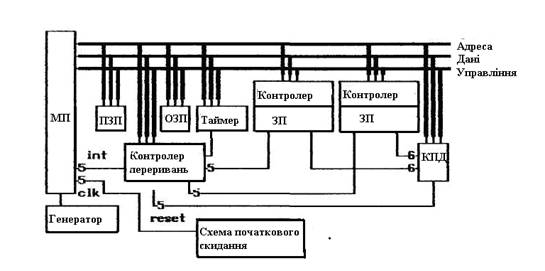

Узагальнена логічна структура мікропроцесорної системи МПС наведена на мал. 3.

Мал.1. Узагальнена логічна структура МП – системи.

Скорочення: МП - мікропроцесор,

ОЗП- оперативний запам’ятовуючий пристрій,

ПЗП – постійний запам’ятовуючий пристрій,

ЗП – зовнішній пристрій,

КПД – контролер прямого доступу до пам’яті.

МП здійснює цифрову обробку даних, здійснює адресацію команд і операндів, що зберігаються в пам'яті за допомогою шин адреси, даних і управління.

В постійному запам’ятовуючому пристрої (ПЗП) зберігаються системні програми, необхідні для управління процесом обробки даних.

В оперативному запам’ятовуючому пристрої (ОЗП) зберігаються прикладні програми, дані і результати обчислень.

Робота МП синхронізується тактовими сигналами СLК, що поступають на його входи від генератора тактової частоти ( синхронізації).

Схема початкового скидання виробляє сигнал RESET (СКИДАННЯ) мікропроцесора на основі аналізу напруг на виході блоку живлення (включення живлення) або при примусовій зупинці роботи МПС з клавіатури.

Контролери — пристрої, що забезпечують обмін даними різних ЗП, мікропроцесором і ОП. Контролер переривань - якій аналізує сигнали (запити на переривання), які надходять до МПС від ЗП (зовнішні переривання) або мікропроцесора ( внутрішні переривання) та організує відгук ( або реакцію) МПС на переривання.

Контролер прямого доступу до пам'яті призначений для обміну даними між ЗП та ОП без участі мікропроцесора.

До складу МПС можуть входити:

- шинний контролер, призначений для сполучення пристроїв з системною шиною по паралельному інтерфейсу;

- послідовного інтерфейсу, призначений для побудови багатопроцесорних систем або сполучення джерел і приймачів сигналів, що не збільшують навантаження на системний інтерфейс;

- спеціалізований процесор арифметичної обробки сигналів (співпроцесор);

- ПЗП команд і констант;

- ОЗП операндів.

Для забезпечення роботи МПС до її системного інтерфейсу можна підключати пристрої для спеціалізованої обробки арифметичних алгоритмів (таких, як швидке перетворення Фур`є, десяткова корекція) і пристрої обробки аналогових сигналів.

Як пристрої для обробки аналогових сигналів використовують аналого-цифрові (АЦП) і цифроаналогові (ЦАП) перетворювачі, що забезпечують безпосереднє сполучення цифрового пристрою обробки з аналоговими сигналами датчиків і приймачів.

Існує три способи передачі інформації:

- програмно-управляюча передача даних, що ініціюється процесором;

- програмно-управляюча передача, що ініціюється запитами на переривання від зовнішнього пристрою;

- прямий доступ до пам'яті (ПДП).

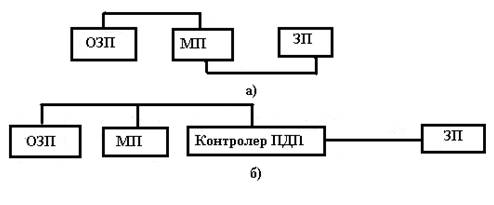

Мал.4. Способи передачі цифрової інформації

При програмно-управляючій передачі, як це показано на мал. 4 а), передача слів відбувається через регістри процесора: слово даних через контролер зовнішнього пристрою надходить до внутрішнього регістра мікропроцесора (акумулятора) і в залежності від потреб подальшої обробки надходить до ОЗП.

При програмно-управляючій передачі даних МП на під час цієї операції відволікається від виконання основної програми, що веде до зниження продуктивності МП системи. Крім того, швидкість передачі даних через МП може виявитися недостатньою для роботи з високошвидкісними ЗП.

Відрізняються перший і другий спосіб передачі даних тільки ініціатором: при першому способі – це процесор ( наприклад, при виконанні команди програми, яка потребує дані з зовнішнього пристрою), при другому – це зовнішній пристрій, сигнал від якого має назву – переривання.

Прямим доступом до пам'яті називається обмін даними, що забезпечує автономну передачу даних між ОЗП і ЗП ( без участі мікропроцесора).

Прямий доступ до пам'яті збільшує граничну швидкість введення/виведення інформації і загальну продуктивність МПС, робить її більш пристосованою для роботи в системі реального часу.

Прямим доступом до пам'яті управляє контролер ПДП, що виконує наступні функції:

- управління передачею даних між ОЗП і ЗП, що ініціюється процесором або ЗП.

- визначення розміру блоку даних, що передаються та області пам'яті, куди записуються дані;

- визначення адреси чарунок ОЗП, що беруть участь в передачі;

- підрахунок кількості байт, що передані через інтерфейс та визначення моменту завершення операції введення/виведення.

Функціонування МПС – це процес, якій складається з виконання команд та обміну даними.

Процес функціонування МПС зводиться до наступної послідовності дій:

отримання даних від різних зовнішніх пристроїв (з клавіатури, від дисплеїв, з каналів зв'язку, від різного типу зовнішніх запам’ятовуючих пристроїв (дискети, флеш-карти, вінчестери)),

обробка даних і

видача результатів обробки на зовнішні пристрої (ЗП).

При цьому дані від ЗП, що підлягають обробці, можуть поступати і в процесі їх обробки.

Оперативна пам'ять (ОЗП) зберігає і видає по запитах команди програми, яку виконує мікропроцесор, різні дані (початкові, проміжні та кінцеві результати обробки);

Мікропроцесор видає на шину адреси номер (адресу) чарунки ОП, в якій записана чергова команда, і по шині управління в ОП поступають сигнали, що забезпечують читання вмісту цієї чарунки. Чергова команда через шину даних передається в мікропроцесор. Тут команда розшифровується.

Якщо дані, які необхідні для виконання цієї команди, знаходяться в регістрах мікропроцесора, то мікропроцесор приступає до виконання вказаною в команді операції.

Якщо при розшифровці команди з'ясується, що дані, що беруть участь в операції, знаходяться в ОП, то мікропроцесор виставляє на шину адреси адресу чарунки, де зберігаються ці дані; після видачі даних з ОП мікропроцесор приймає їх через шину даних, потім виконується операція над даними.

Після завершення поточної команди на шину адреси видається адреса наступної команди, і описаний процес повторюється.

Обмін даними з ЗП може здійснюється таким чином.

Мікропроцесор, виконуючи команду введення, подає на контролер відповідні керівні сигнали; дані з ЗП приймаються в регістр контролера, потім вони контролером видаються на шину даних. Далі ці дані з шини даних приймаються в мікропроцесор. Потім в процесі виконання відповідної команди вони передаються в ОП.

Аналогічно відбувається обмін даними у зворотному напрямі — від ОП до ЗП. По відповідній команді програми здійснюється прийом з ОП в мікропроцесор даних, що підлягають передачі на ЗП, після чого по одній з наступних команд ці дані видаються на шину даних і через контролер обміну передаються на ЗП.

Описаний процес обміну припускає, що моменти обміну даними відомі наперед вже на етапі програмування, і в програмі передбачаються в певних місцях відповідні команди.

Моменти обміну можуть визначатися і самим ЗП. В таких випадках ЗП подає в мікропроцесор певні сигнали і переводить його в стан переривання. Перебуваючи в стані переривання мікропроцесор припиняє виконання основної програми і переходить до виконання команд іншої програми (перериваючої програми), зберігається в ОП. Після закінчення перериваючої програми мікропроцесор повертається до виконання основної програми.

Описані способи забезпечують низьку швидкість обміну, і застосовувати їх доцільно при обміні даними з низькошвидкісними ЗП.

При роботі з високошвидкісними ЗП (такими, як що запам'ятовують пристрої на дисках і ін.) використовується так званий метод прямого доступу до пам'яті (ПДП). В цьому режимі мікропроцесор відключається від шин адреси і даних, надаючи їх в розпорядження ЗП для безпосереднього обміну даними з ОП (без участі мікропроцесора). Обмін при цьому організовується спеціальним контролером ПДП.

У режимі ПДП ЗП обмінюється з ОП не битами або байтами даними, а великими блоками даних. В контролер ПДП мікропроцесор заздалегідь поміщає інформацію, необхідну для управління обміном (адреса чарунки ОП, куди записується або звідки прочитується перше належне обміну слово, кількість слів в блоці і ін.). В процесі обміну контролер ПДП видає на шину адреси адресу чарунки ОП, після закінчення передачі слова між ОП і ЗП через шину даних контролер ПДП збільшує на одиницю значення адреси, видаваної на шину адреси. Після завершення передачі заданої кількості слів контролер ПДП припиняє обмін, інформуючи про це мікропроцесор. Останній відновлює зв'язок з шинами адреси і даних і продовжує виконання програми.

Під організацією мікро-ЕОМ розуміють склад її програмно-апаратних засобів, зв'язки між ними і їх функціональні характеристики. Мікросистеми мають багаторівневу ієрархічну організацію з багатьма складовими компонентами на кожному рівні. З нижнім рівнем функціонального опису МПС і її складових пов'язано поняття фізичної організації мікро-ЕОМ - її функціональна схема. Термін "логічна організація" відноситься до більш високих рівнів опису мікро-ЕОМ. Так, логічна організація на рівні апаратури - це склад, функціональні зв'язки і характеристики взаємодії апаратних модулів в процесі виконання різних задач, які звичайно називають структурною схемою або структурою. Про логічну організацію на рівні програмного забезпечення (ПО) говорять як про обчислювальне середовище і її особливості.

Кінцева мета проектування МПС - створення працездатного і оптимального виробу на базі одного або декількох МП. Можливість її досягнення визначається в першу чергу вибором раціонального співвідношення між програмними і апаратними засобами. Для цього вводиться поняття архітектури.

Мікросистемам, побудованим па основі мікропроцесорних комплектів (МПК) молодшого покоління, властива більш проста архітектура, що було важливе для інтегральної технології минулого десятиріччя. Проте обчислювальні можливості і швидкодія цих систем, як правило, були низькі. Удосконалення технологічних прийомів дозволило збільшити ступінь інтеграції апаратури і перейти до складної 16-розрядної архітектури з віртуальною пам'яттю, що забезпечує паралельну обробку багатьох задач в реальному масштабі часу.

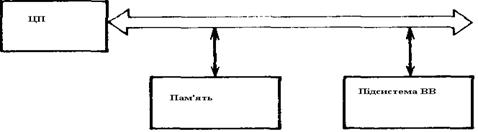

Мікросистема (МС) складається з побудованого на базі МПК центрального процесора (ЦП), основної пам'яті для зберігання програм і даних, а також підсистеми уведення-виведення для зв'язку МПС із зовнішньою апаратурою. Задача управління МС покладається на ЦП, який пов'язаний з пам'яттю і підсистемою ВВ через канали пам'яті і ВВ відповідно. Центральний процесор прочитує з пам'яті МС команди, які утворюють програму, і декодує їх. Відповідно до результату декодування команд він здійснює вибірку даних з пам'яті МС і портів введення, обробляє їх і пересилає назад в пам'ять або порти виводу підсистеми ВВ. Існує також можливість ВВ даних з пам'яті на зовнішні пристрої і назад, минаючи ЦП. В такому випадку обмін даними виконується через канал прямого доступу до пам'яті (ПДП), управління яким покладається на підсистему ВВ. Іноді виділяються ресурси підтримки режиму реального часу, в найпростішому випадку що розділяються процесором і підсистемою ВВ.

Мал.5 Базова організація мікро-ЕОМ

Кожний рівень організації мікро-ЕОМ і будь-яка її складова частина мають достатньо складну внутрішню структуру, деталізація якої приводить до появи різних типів структур і обчислювальних середовищ. Відповідно до принципу програмного управління, що використовується в МС, їх організація в значній мірі визначається методологією побудови великих обчислювальних систем. Проте через особливості виробництва МПК БІС і їх вживання організація МС придбала ряд рис, не властивих великим ЕОМ.

Перепечатка материалов без ссылки на наш сайт запрещена