Курсовая работа: Исследование арифметико–логического устройства для выполнения логических операций

Курсовая работа: Исследование арифметико–логического устройства для выполнения логических операций

КУРСОВАЯ РАБОТА

дисциплина «Вычислительная техника»

на тему

Исследование арифметико–логического утройства для выполнения логических операций

Выполнил: Бородулин

Пермь, 2010г.

СОДЕРЖАНИЕ

ВВЕДЕНИЕ

1 ОПИСАНИЕ АРИФМЕТИКО–ЛОГИЧЕСКОГО УСТРОЙСТВА

2 ОПИСАНИЕ БЛОКА РЕГИСТРА

3 ПРОЕКТИРОВАНИЕ СУММАТОРА

ЗАКЛЮЧЕНИЕ

СПИСОК ЛИТЕРАТУРЫ

ВВЕДЕНИЕ

Рассмотрим особенность реализации арифметико-логического устройства компьютера на примере проектирования АЛУ для выполнения логических операций. Классическая ЭВМ состоит из трех основных устройств: арифметико-логического устройства, устройства управления и запоминающего устройства. Рассмотрим особенность структуры арифметико-логического устройства. В современных ЭВМ арифметико-логическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер. Однако знание структуры и принципов работы АЛУ весьма важно для понимания работы компьютера в целом.

В микропроцессорной системе есть арифметико-логическое устройство для выполнения логических операций над числами (операндами, словами) выполняются в главной части процессора - арифметико-логическом устройстве (АЛУ)

Все арифметические действия с двумя числами (сложение, вычитание, умножение, деление) сводятся в АЛУ к операции сложения или вычитание.

Упрощенная структура ЭВМ содержит следующие основные устройства: арифметико-логическое устройство, память, управляющее устройство, устройство ввода данных в машину, устройство вывода из нее результатов расчета и пульт ручного управления.

В данном курсовом проекте я буду рассматривать работу многофункционального арифметико-логического устройства (АЛУ). АЛУ для выполнения логических операций, они служат для выполнения арифметических и логических преобразований над словами, называемыми в этом случае операндами, а также арифметические операции.

Быстродействие АЛУ во многом определяет производительность процессора.

Целью данной курсовой работы является исследование и принцип работы арифметико-логического устройства для выполнения логических операций.

Основными задачами являются:

1. исследовать арифметико-логического устройства для выполнения логических операций;

2. привести условно–графическое обозначение микросхемы регистра, входящего в состав арифметико-логического устройства;

3. описать принцип работы арифметико-логического устройства;

4. рассмотреть логическую схему регистра;

5. проанализировать принцип записи, чтения и хранения информации в регистре;

6. указать на схеме сигналы, передаваемы на информационные входы регистра; указать номера и типы входов, на которые подаются управляющие сигналы в режиме записи; указать на выходах двоичное число, зафиксированное в регистре после выполнения сдвига влево на 4 разряда; указать номер входа, на который поступают импульсы сдвига;

7. проанализировать работу сумматора входящего в арифметико-логического устройства;

8. построить логическую схему сумматора;

9. описать принцип работы сумматора

1. ОПИСАНИЕ АРИФМЕТИКО–ЛОГИЧЕСКОГО УСТРОЙСТВА

Арифметико-логическое устройство (АЛУ) - центральная часть процессора, выполняющая арифметические и логические операции.

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление...). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ...). Операции над битами обычно подразумевают сдвиги.

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части:

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

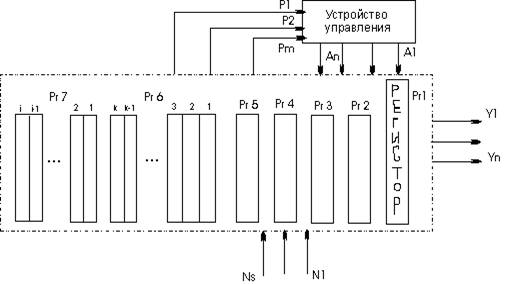

Рисунок. 1 Структурная схема АЛУ

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация, поступающая из оперативной или пассивной памяти N1, N2, ...NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма, которая записывается в виде последовательности микрокоманд A1,A2, ..., Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2,..., Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2,..., рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, ...,уs, в ОЗУ. Функции регистров, входящих в АЛУ: Рг1 – регистр (или сумматоры) - основной регистр АЛУ, в котором образуется результат вычислений; Рг2, РгЗ - регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции); Рг4 - адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата; Ргб - k индексных регистров, содержимое которых используется для формирования адресов; Рг7 - i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся: сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется не сколько различных операций пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

2. ОПИСАНИЕ БЛОКА РЕГИСТРА

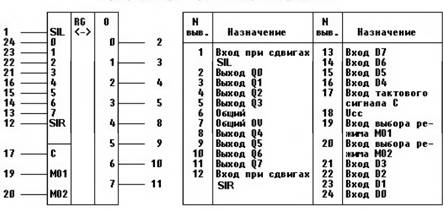

В задании используются универсальные регистры, разрядность которых (n) можно определить по количеству выходов. В регистре к1500ир141 имеется 4 выходов следовательно разрядность регистра (n) будет равна 4 Микросхема к1500ир141 представляет собой регистр, состоящий из 4 D-тиггеров. Выходы М01 и М02 позволяют выбрать один из четырех режимов работы регистра: загрузка данных, хранение данных, сдвиг данных в лево или в право. Все операции (кроме хранения) происходят по положительному перепаду на тактовом входе С. Регистр имеет 2 последовательных входа SIL (вход данных для сдвига в право) и SIR (вход данных для сдвига влево). При напряжении высокого уровня на входах М01 и М02 регистр хранит данные независимо от сигналов на других входах. Условно графическое обозначение микросхемы к1500ир141 представлено на рисунке 2.

Рисунок 2-Условно графическое обозначение микросхемы к1500ир141 и обозначение входов и выходов

Для данной микросхемы существуют 2 способа записи информации последовательный и параллельный. При последовательном способе записи сигнал V должен быть низкого уровня, а код, который записывается, должен поступать на вход D0. С каждым тактовым импульсом М01 входной код продвигается на один разряд в сторону старшего разряда. При параллельном способе записи код подается на входы D4-D1. Запись проводится в паузе между тактовыми импульсами М01 при V=1 импульсом М02. Если после записи число нужно сдвинуть, то регистр переводят в режим сдвига сигналом V=0 и руководят с помощью импульсов М01. При условии, что Q1 - выход младшего разряда, а Q4 - старшего, информация в регистре сдвигает влево (обратной сдвиг). Но он может быть преобразован и в регистр со сдвигом вправо (прямой сдвиг). Для этого необходимо выполнить следующие внешние соединения: D3 с Q4, D2 с Q3, D1 с Q2. Код записывают по входу D4 при V = 1, а руководят регистром тактовыми импульсами М02. Таким образом, в рассмотренном регистре выполняются условия как прямого, так и обратного сдвигов. Регистр имеет выходы от всех разрядов, что позволяет считывать записанный код как в последовательной, так и в параллельной формах представления информации во времени.

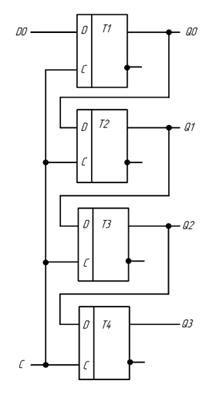

Рисунок 3 – Логическая схема регистра к1500ир141

Регистр к1500ир141 является универсальными (регистр общего назначения), он может использоваться для временного хранения любых данных, при этом позволять работать как с регистром целиком, так и отдельно и с каждой его половиной, (регистры АН, ВН, СН, DH -- старшие (High) байты, а регистры AL, BL, CL, DL -- младшие (Low) байты, соответствующих двухбайтовых регистров). Но также универсальный регистр к1500ир141 может использоваться и как специальный при выполнении некоторых конкретных команд программы.

В данной работе требуется рассчитать сигналы на выходе микросхемы к1500ир141 после подачи на вход двоичного сигнала 1110 при сдвиге влево на 4 разряда. При сдвиге влево происходит смещение операнда на более уровень а на его место устанавливается сигнал 0. Процесс сдвига показан в таблице 2.

Таблица 2 – процесс сдвига влево на 4 разряда.

Вход триггера Q4 Q3 Q2 Q1

Число сдвига 1 1 1 0

Число сдвига 1 1 1 0

Число после 1-го сдвига 1 1 0 0

Число после 2-го сдвига 1 0 0 0

Число после 3-го сдвига 0 0 0 0

Число после 4-го сдвига 0 0 0 0

Результатом сдвига будет двоичное число 0000.

3. ПРОЕКТИРОВАНИЕ СУММАТОРА

Параллельные четырехразрядных сумматоры предназначены для одновременного суммирования двух четырехразрядных чисел и характеризуются различными способами передачи сигналов переноса от младших разрядов сумматора к старшим.

Четырехразрядные сумматоры выполняют операцию арифметического сложения двух четырехразрядных двоичных чисел. Количество входов и выходов сумматора определяется разрядностью слагаемых. Быстродействие сумматора определяется временами распространение сигнала через все его элементы, и потому оно значительно ниже быстродействия элементов.

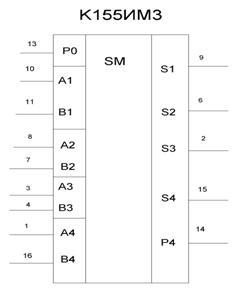

Рисунок 4 – Двоичный сумматор К555ИМ3

13-ввход переноса; 10,11,8,7,3,4,1,16-входы ;12-общий; 9,6, 2, 15-выходы суммы; 5-UЛ выход переноса.

Необходимо спроектировать сумматор, который имеет модель типа К555ИМ3. Для того чтобы узнать сигналы на выходе четырехразрядного сумматора К555ИМ3 при подаче на входы сигналов 0100 и 1101, необходимо сложить эти числа.

С = 0011 - первое слагаемое

+

D = 1100 - второе слагаемое

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

С+D = 01111 - сумма

Таблица 1 – сигналы на сумматоре поле выполнения операции

Сумма этих чисел и будет на выходе сумматора. Сигналы на входе и выходе сумматора показаны на рисунке 5

| DD2 | A4 | 0 | P4 | 0 |

| B4 | 1 | |||

| A3 | 1 | S4 | 1 | |

| B3 | 1 | |||

| A2 | 1 | S3 | 1 | |

| B2 | 1 | |||

| A1 | 0 | S2 | 1 | |

| B1 | 1 | |||

| P0 | 0 | S1 | 1 |

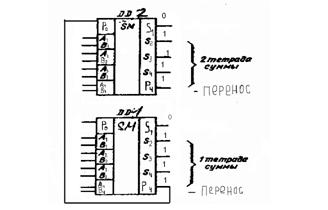

Для построение 8 разрядного сумматора необходимо соединить 2 четырехразрядных сумматора К555ИМ3, способом, показанным на рисунке 5

Рисунок 5 – Способ построения 8 разрядного сумматора на базе двух четырехразрядных сумматора К555ИМ3

При построении сумматора для восьмиразрядных чисел нужно учитывать, что на входы этого сумматора слагаемые поступают параллельно, а перенос между разрядами передается последовательно.

Для расчета сигналов на выходе восьмиразрядного сумматора при подаче на вход сигналов 11110000 и, 00000001 необходимо сложить эти числа.

Выполним сложение двух восьмиразрядных чисел С и D.

С = 1111 0000 - первое слагаемое

+

D = 0000 001 - второе слагаемое

_

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _

_

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _

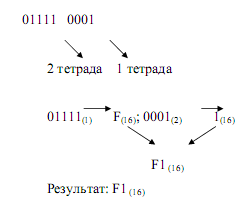

С+D = 01111 0001 - сумма

2 тетрада 1 тетрада

1 тетрада – 4 младших разряда числа

2 тетрада – 4 старших разряда числа

Для сложения старшие разряды чисел С и D поступают на информационные входы микросхемы DD2, а цифры младших разрядов – на входы DD1 параллельным способом. Сигналы на выходах и входах микросхему после выполнения операции показаны на таблице 2

Таблица 2 – Значения сигналов на выходах и входах микросхему К555ИМ3 после выполнения сложения 11110000 и 00000001.

| DD2 | A4 | 0 | P4 | 0 |

| B4 | 1 | |||

| A3 | 0 | S4 | 1 | |

| B3 | 1 | |||

| A2 | 1 | S3 | 1 | |

| B2 | 0 | |||

| A1 | 1 | S2 | 1 | |

| B1 | 0 | |||

| P0 | 1 | S1 | 1 | |

| DD1 | A4 | 0 | P4 | 0 |

| B4 | 1 | |||

| A3 | 0 | S4 | 0 | |

| B3 | 1 | |||

| A2 | 1 | S3 | 0 | |

| B2 | 0 | |||

| A1 | 1 | S2 | 0 | |

| B1 | 0 | |||

| P0 | 0 | S1 | 1 |

Выполним перевод результата сложения из двоичной системы счисления в десятичную, восьмеричную и шестнадцатеричную системы счисления. Для удобства сначала переведем число в шестнадцатеричную систему счисления, затем в десятичную и восьмеричную системы счисления.

Для перевода двоичного числа в шестнадцатеричную систему счисления необходимо разложить число на тетрады и перевести его в шестнадцатеричную систему счисления, затем сложить их согласно приоритету тетрада.

Для перевода в десятичную систему счисления необходимо разложить шестнадцатеричное число на разряды, затем каждый разряд, начиная с младшего умножить на 16 в степени старшинства разряда начиная с нулевой степени, после чего сложить результат.

f1(16) = 15* 161 + 1*160=241(10)

Результат: 241(10)

Для перевода из десятичной системы счисления в восьмеричную необходимо разделить десятичное число на 8 до деления без остатка, результатом будет число сложное из остатков от деления, начиная с последнего остатка

|

|

|

|

|

240 30 8 |

|

|

| 6 |

Результат 361(8)

Результаты расчетов:

![]()

![]()

![]() 011110001 (2)

24110)

361 F1(16)

011110001 (2)

24110)

361 F1(16)

Заключение

Исследуя в данной курсовой работе многофункциональное арифметическо-логическое устройство, я пришел к выводу, что АЛУ реализует важную часть процесса обработки данных вычислительных операций. В результате работы были рассмотрены схемы обобщенной структуры АЛУ процессоров, построены структурная и логическая схемы, был произведен анализ и построение блоков, составляющих важную часть АЛУ. Исходя из задания, спроектирован регистр левого сдвига К1500ИР141, приведена логическая схема четырехразрядного регистра К1500ИР141, перечислены основные функции, выполняемые заданным регистром. регистра, на схеме указаны сигналы, подаваемые на информационные входы регистра. Спроектирован и рассчитан четырехразрядный двоичный сумматор. Приведено условное графическое обозначение микросхемы данного двоичного сумматора. Описан принцип работы. Построена логическая схема четырехразрядного сумматора последовательного действия на базе полусумматоров и логических элементов ИЛИ. Приведена схема соединения микросхем

СПИСОК ЛИТЕРАТУРЫ

1. Калабеков Б.А., Мамзелев И.А. Цифровые устройства и микропроцессорные системв. – М.: Радио и связь. 2004.

2. Коган И.Л., Гитлиц Э.В., Еремина О.В. Микропроцессорные устройства. Сборник методических указаний. – М.: ВЗТС, 2003.

3. Мышляева И.М. Цифровая схемотехника. Учебник для сред. проф. образования. – М.: 2005.

4. Основы микропроцессорной техники. Курс лекций/ Новиков Ю.В., Скоробогатов П.К. – М.: 2003.

5. Угрюмов Е. Цифровая схемотехника. – С-Петербург, изд-во «БХВ-Петербург», 2002.

6. Цифровая и вычислительная техника: Уч. для вузов / Э.В. Евреинов, Ю.Т. Бутыльский, И.А. Мамзелев и др.; Под ред. Э.В. Евреинова. - М.: Радио и связь, 1991.

7. Цифровые интегральные микросхемы: Справочник. – 2-е изд., перераб. и доп. – Минск: «Беларусь»: «Полымя», 1996.

Перепечатка материалов без ссылки на наш сайт запрещена