Реферат: Последовательностные функциональные узлы

Реферат: Последовательностные функциональные узлы

Содержание

1. Общая структура последовательностного устройства

2. Синхронные триггеры

3. Порядок синтеза последовательностного устройства

Библиографический список

1. Общая структура последовательностного устройства

Цифровое устройство, в котором состояние выхода зависит не только от того, какие сигналы присутствуют на его входах в данное время, но и от того, какие последовательности сигналов поступали на входы устройства в предшествующие моменты времени, называют цифровым автоматом. Такие устройства за их способность запоминать последовательности входных или выходных сигналов называют также последовательностными устройствами.

![]()

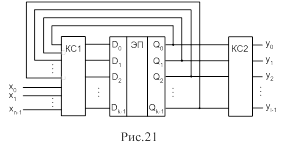

Цифровые автоматы, применяемые в цифровой технике, преимущественно строятся по общей схеме, приведенной на рис.1. Такие автоматы называют автоматами Мура. На рис.21: ЭП – элементы памяти (регистр) c входами D0,...,Dk-1 и выходами Q0,...,Qk-1. КС1 вырабатывает входные сигналы для элементов памяти, используя для этого их текущие состояния выходов (коды Q0,...,Qk-1) и внешние сигналы x0,...,xn-1 (коды настройки на определенный режим работы, сигналы синхронизации и т.п.). КС2 преобразует внутренние рабочие коды состояния устройства Q0,...,Qk-1 в выходные коды y0,...,yk-1.

Состояния всех входов, элементов памяти и выходов рассматриваются в одинаковые дискретные моменты времени. В зависимости от того, как эти моменты времени определены, последовательностные устройства разделяются на синхронные и асинхронные.

В синхронных устройствах дискретные моменты времени задают специальные синхронизирующие сигналы (импульсы), поступающие от некоторого независимого источника синхронизации. В синхронных последовательностных устройствах, следовательно, длительность рабочего такта задается синхронизирующими сигналами.

В отличие от синхронного, в асинхронном последовательностном устройстве дискретные моменты времени определяются моментами изменения состояния входа или состояния памяти, а длительность рабочих тактов определяется интервалом времени, в течение которого состояние автомата не меняется.

Таким образом, работу цифрового автомата Мура (рис.1) можно определить следующими логическими уравнениями

Qt+1=f1(Qt,X t), Y t=f2(Qt), (14)

где Qt – k-разрядное число, определяющее состояние памяти автомата в дискретное время t (текущее состояние памяти); X t – n-разрядное число, определяющее состояние входов в дискретное время t (текущее состояние входов); Qt+1 – k-разрядное число, определяющее состояние памяти в дискретное время t+1 (последующее состояние памяти); Y t – l-разрядное число, определяющее состояние выходов в дискретное время t (текущее состояние выходов).

2. Синхронные триггеры

В качестве элементов памяти в схеме цифрового автомата рис.1 используются триггеры, включенные определенным образом в структуру памяти для обеспечения выполнения его функций.

Используемые в цифровой технике триггеры представляют собой электронные схемы, имеющие два устойчивых состояния. Эти состояния устанавливаются при подаче соответствующей комбинации сигналов на входы триггера и сохраняются после окончания действия этих сигналов.

Состояние триггера описывается значением выходного сигнала Q. Это состояние определяется (задается) комбинацией входных сигналов на информационных входах триггера. Если при изменении сигналов на информационных входах соответствующее изменение Q, т.е. переключение триггера происходит только при поступлении синхронизирующего сигнала (импульса) на специальный вход синхронизации С, то триггер называется синхронным. Триггеры могут переключаться по уровню или по фронту синхроимпульса.

Триггеры, переключающиеся по уровню, могут изменять свое состояние в течение длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих информационных сигналов, т.е. могут переключиться несколько раз за время действия одного синхроимпульса. В течение паузы между синхроимпульсами состояние такого триггера сохраняется при любых изменениях информационных сигналов.

Триггеры, переключающиеся по фронту, изменяют свое состояние при поступлении на синхронизирующий вход соответствующего фронта синхроимпульса (положительного или отрицательного). За время действия одного синхроимпульса триггер, синхронизируемый фронтом, может переключиться только один раз.

В асинхронных триггерах отсутствует вход синхронизации. Поэтому переключение асинхронных триггеров происходит, как только на информационные входы поступает соответствующая переключающая комбинация сигналов.

В цифровой технике наиболее часто используются SR-, JK-, D-, T-триггеры. Обозначающие тип триггера буквы раскрывают функциональное назначение информационных (управляющих) входов триггера:

S – вход установки в состояние 1;

R – вход установки в состояние 0;

J – вход переключения из состояния 0 в состояние 1;

K – вход переключения из состояния 1 в состояние 0;

D – информационный вход для установки состояния 1 или 0;

T – вход инвертирования состояния триггера (счетный вход).

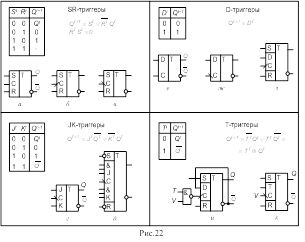

Функциональные возможности триггера описывают его характеристическая таблица (таблица состояний) и характеристическое уравнение. Для перечисленных типов триггеров они приведены на рис.2. Таблица состояний и уравнение определяют логическую зависимость последующего состояния триггера Qt+1 от текущих значений сигналов на информационных входах и текущего состояния триггера Qt.

![]()

SR-триггер. При S = R = 0 триггер работает в режиме хранения, т.е. сохраняет ранее установленное состояние Qt+1 = Qt. При S = 1, R = 0 триггер устанавливается в состояние Qt+1 = 1, а при S = 0, R = 1 – в состояние Qt+1 = 0. Комбинация входных сигналов S = R = 1 (установка 1 и 0 одновременно) является запрещенной, так как приводит к непредсказуемому состоянию триггера после поступления синхроимпульса. Во избежание возникновения сбоев комбинацию S = R = 1 исключают, поэтому она является нереализуемой.

Характеристическое уравнение SR-триггера, приведенное на рис.2, легко получить путем минимизации логической функции Qt+1(St,Rt,Qt) с использованием карты Карно.

Синхронные SR-триггеры могут синхронизироваться уровнем, положительным фронтом, отрицательным фронтом (рис.2,а,б,в) синхросигнала.

JK-триггер получен путем

усовершенствования SR-триггера. JK-триггер реализует все режимы работы SR-триггера, но не имеет запрещенных

комбинаций сигналов на информационных входах. При воздействии на информационные

входы сигналов J = K = 1 триггер инвертирует свое

состояние после поступления синхроимпульса ![]() , то есть работает в режиме

счета синхроимпульсов.

, то есть работает в режиме

счета синхроимпульсов.

Поэтому JK-триггер является универсальным триггером и выпускается в виде готовых микросхем, которые предназначены для применения в нетиповых регистрах и счетчиках. JK-триггеры в интегральном исполнении могут иметь несколько входов J и K, а также асинхронные входы принудительной установки триггера в единичное или нулевое состояние. Пример такого триггера приведен на рис.2,д. Логические сигналы на информационных входах J и K перемножаются, что обозначено знаком конъюнкции &; асинхронные сигналы для установки 1 или 0 (входы S и R) должны иметь низкий уровень, что обозначено кружком. Такие триггеры имеют расширенные логические возможности, и их использование в цифровых устройствах позволяет уменьшить аппаратные затраты.

D-триггер имеет таблицу состояний, в которой отсутствует состояние, соответствующее режиму хранения, триггер всегда воспринимает значение сигнала на входе D с задержкой на один период синхронизации Qt+1= Dt. Поэтому D-триггер является триггером задержки информации, поступающей на информационный вход D.

D-триггеры с переключением по уровню синхроимпульса (рис.2,е) применяются в регистрах памяти. Триггеры с переключением по положительному или отрицательному фронту (рис.2,ж,з) используются в регистрах сдвига, в счетчиках импульсов и т.п., в таком случае они, как правило, имеют входы принудительной асинхронной установки в 1 или 0 (рис.2,з).

T-триггер называется счетным триггером. Состояние его выхода меняется на противоположное при поступлении на вход счетного сигнала T = 1 и сохраняется неизменным при T = 0. T-триггер можно получить из JK-триггера, определив J = K = 1, или из D-триггера (рис.2,и). Условное

графическое обозначение T-триггера показано на рис.2,к. T-триггеры применяются для построения

счетчиков импульсов, поэтому они имеют асинхронные входы (прямые – R и S или инверсные – ![]() и

и![]() ) для сброса триггера в

нулевое состояние и установки единицы.

) для сброса триггера в

нулевое состояние и установки единицы.

В произвольном

последовательностном устройстве любой триггер, как элемент памяти, должен

обеспечивать выполнение следующих четырех функций для дискретных моментов

времени t и t+1:![]()

- сохранить нулевое

состояние ![]()

- сохранить единичное

состояние ![]()

- перейти из нулевого

состояния в единичное ![]()

- перейти из единичного

состояния в нулевое ![]() .

.

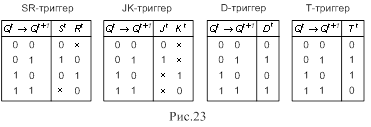

Каждая функция переходов триггера FQ может быть реализована лишь при определенных текущих (в дискретное время t) значениях сигналов на информационных входах. Эти значения получаются из характеристического уравнения триггера. Если задать в нем значения Qt и Qt+1, то путем перебора подстановок можно найти текущие значения управляющих сигналов, при которых левая и правая части характеристического уравнения одинаковы, т.е. реализуется заданное значение функции переходов FQ.

![]()

![]()

Значения информационных сигналов, реализующие все значения функции переходов для основных типов триггеров, приведены в таблицах на рис.3. Такие таблицы носят название – таблица переходов или словарь переходов триггера.

3. Порядок синтеза последовательностного устройства

Любое последовательностное устройство можно выполнить в виде синхронного или асинхронного автомата. Асинхронные автоматы могут быть получены из синхронных с помощью некоторых преобразований, описанных в [1]. Поэтому ниже рассмотрены синхронные последовательностные устройства с малым объемом памяти (регистры, счетчики, генераторы числовых последовательностей) и устройства смешанного типа (синхронные с асинхронной установкой некоторого внутреннего состояния).

В общей схеме последовательностного устройства (рис.1) КС1 реализует логическое уравнение f1 (14) и определяет последующее состояния памяти Qt+1 в зависимости от ее текущего состояния Qt и текущего состояния входов Xt. КС2 является преобразователем внутреннего кода Qt в выходной код автомата Yt. Логику работы КС2 задает уравнение f2 (14). Следовательно, синтез устройства, общая структура которого показана на рис.21, сводится к определению количества элементов памяти, их типов и к синтезу комбинационных схем КС1 и КС2 в выбранном логическом базисе. Процесс синтеза состоит из нескольких этапов [3].

1. Определение количества состояний устройства, построение таблицы или графа состояний, построение временных диаграмм.

Чаще всего функционирование последовательностного устройства представляется в виде таблицы состояний для внутренних переменных Q и внешних переменных y, либо в виде графа состояний.

Таблица состояний содержит все комбинации k-разрядного внутреннего кода Qk-1,...,Q0, которые для определенных комбинаций входных переменных xn-1,...,x0 должен формировать автомат в заданном порядке, и соответствующие им все комбинации l-разрядного выходного кода yl-1,...,y0.

Граф состояний – ориентированный граф, вершины которого соответствуют состояниям, а дуги – переходам между ними (рис.24, 27). Состояния автомата и соответствующие им выходные сигналы записываются в вершинах графа (в кружках). Каждой дуге графа приписывается значение входного сигнала (сигналов) xi, которое задает переход в другое состояние. В графе автомата не должно существовать двух дуг с одинаковыми входными сигналами, исходящих из одной и той же вершины (условие однозначности). На основании графа автомата можно составить таблицу состояний и таблицу переходов.

2. Выбор элементов памяти (триггеров), определение логических функций управления информационными входами триггеров.

Выбор типа триггера осуществляется путем сопоставления логики работы (таблицы состояний) проектируемого устройства и логики работы (таблицы переходов) триггеров различных типов. В тех случаях, когда выбор типа триггера не очевиден, используют установленные критерии (минимум аппаратных затрат, тип элементной базы и т.п.).

После выбора типа

триггера необходимо определить логические функции управления всеми

информационными входами всех триггеров. В совокупности эти функции определяют

структуру комбинационной схемы КС1 (рис.1). Таблица истинности для функций

управления информационными входами триггеров составляется по таблице (графу)

состояний последовательностного устройства (из которой для каждого состояния

устройства и для каждого i-го

триггера находится подлежащая реализации функция переходов ![]() ) и словарю переходов

триггера (из которого для полученных функций переходов i-го триггера определяются требуемые для их реализации сигналы

на информационных входах).

) и словарю переходов

триггера (из которого для полученных функций переходов i-го триггера определяются требуемые для их реализации сигналы

на информационных входах).

3. Минимизация функций управления информационными входами, построение схемы последовательностного устройства.

Минимизация найденных на втором этапе синтеза логических функций управления информационными входами может быть выполнена рассмотренным ранее методом с помощью карт Карно. Затем осуществляется переход в заданный базис, после чего составляется комбинационная схема КС1.

Комбинационная схема КС2 (рис.1) может быть синтезирована как преобразователь внутреннего кода в выходной код для всех состояний последовательностного устройства.

Библиографический список

1.Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов. СПб.: Политехника, 1996.

2.Угрюмов Е.П. Цифровая схемотехника. СПб.: БХВ-Петербург, 2001.

3.Проектирование импульсных и цифровых устройств радиотехнических систем: Учеб. пособие для радиотехнич. спец. вузов / Ю.П.Гришин, Ю.М.Казаринов, В.М.Катиков и др.; Под. ред. Ю.М.Казаринова. М.: Высш. шк., 1985.

4.Потемкин И.С. Функциональные узлы цифровой автоматики. М.: Энергоатомиздат, 1988.

5.Голдсуорт Б. Проектирование цифровых логических устройств: Пер. с англ. М.: Машиностроение, 1985.

Перепечатка материалов без ссылки на наш сайт запрещена